目录

本来不打算写这篇文章,因为它与前端的知识体系比较偏。但是在学习的过程中,了解了生活中的问题, 比如宽带速率、U盘空间大小、断电内存数据丢失等,了解了为什么现代的计算机演变为这个架构, 再比如缓存策略LRU在前端中也有应用, 多花两天时间了解下吧,对计算机的世界有更清晰的认识。

常见问题

- 为什么软件安装需要下载对应的芯片处理器版本?

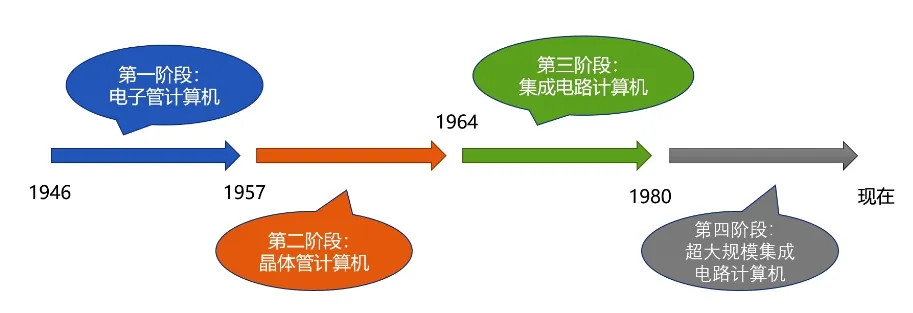

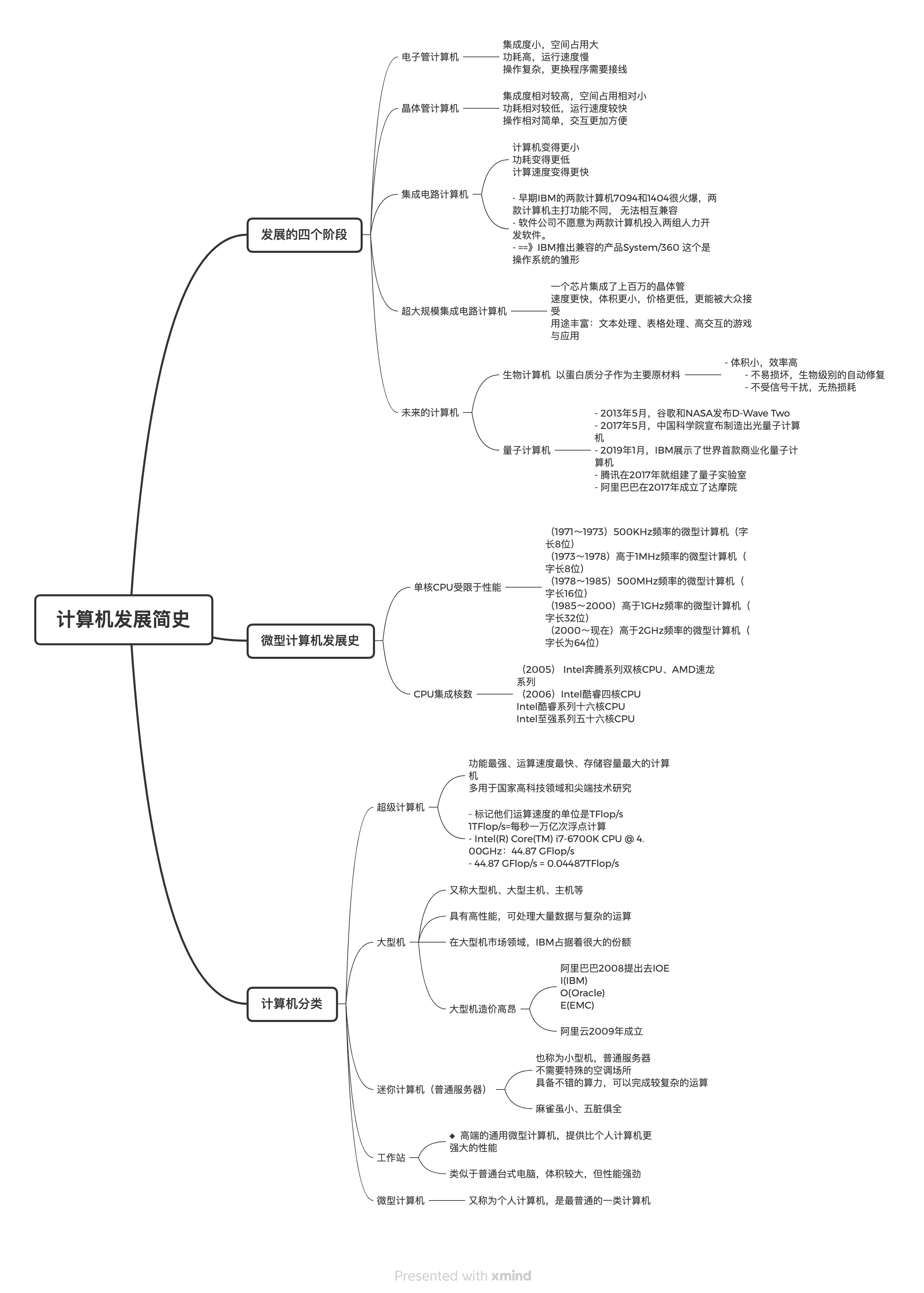

计算机的发展简史

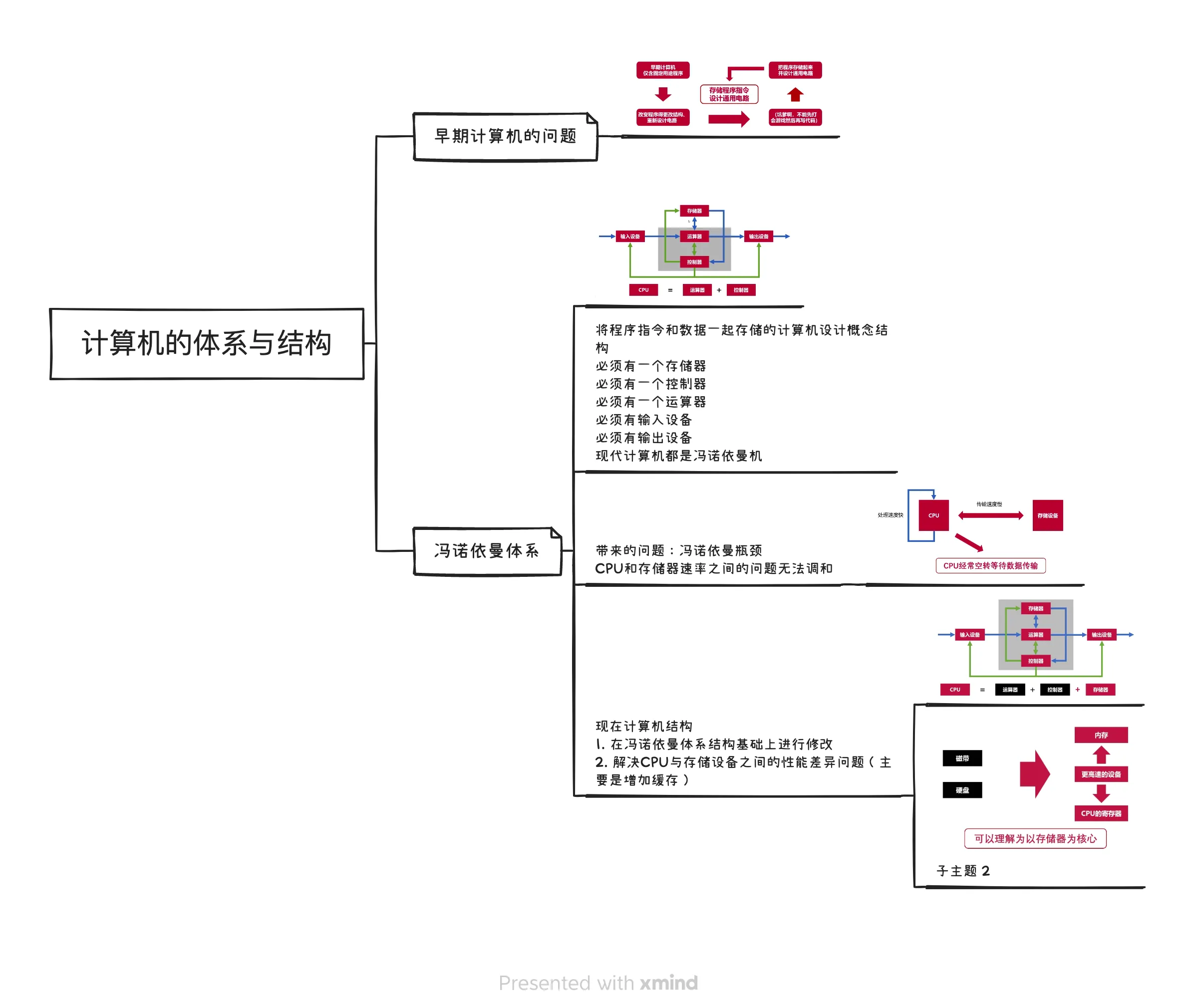

计算机的体系与结构

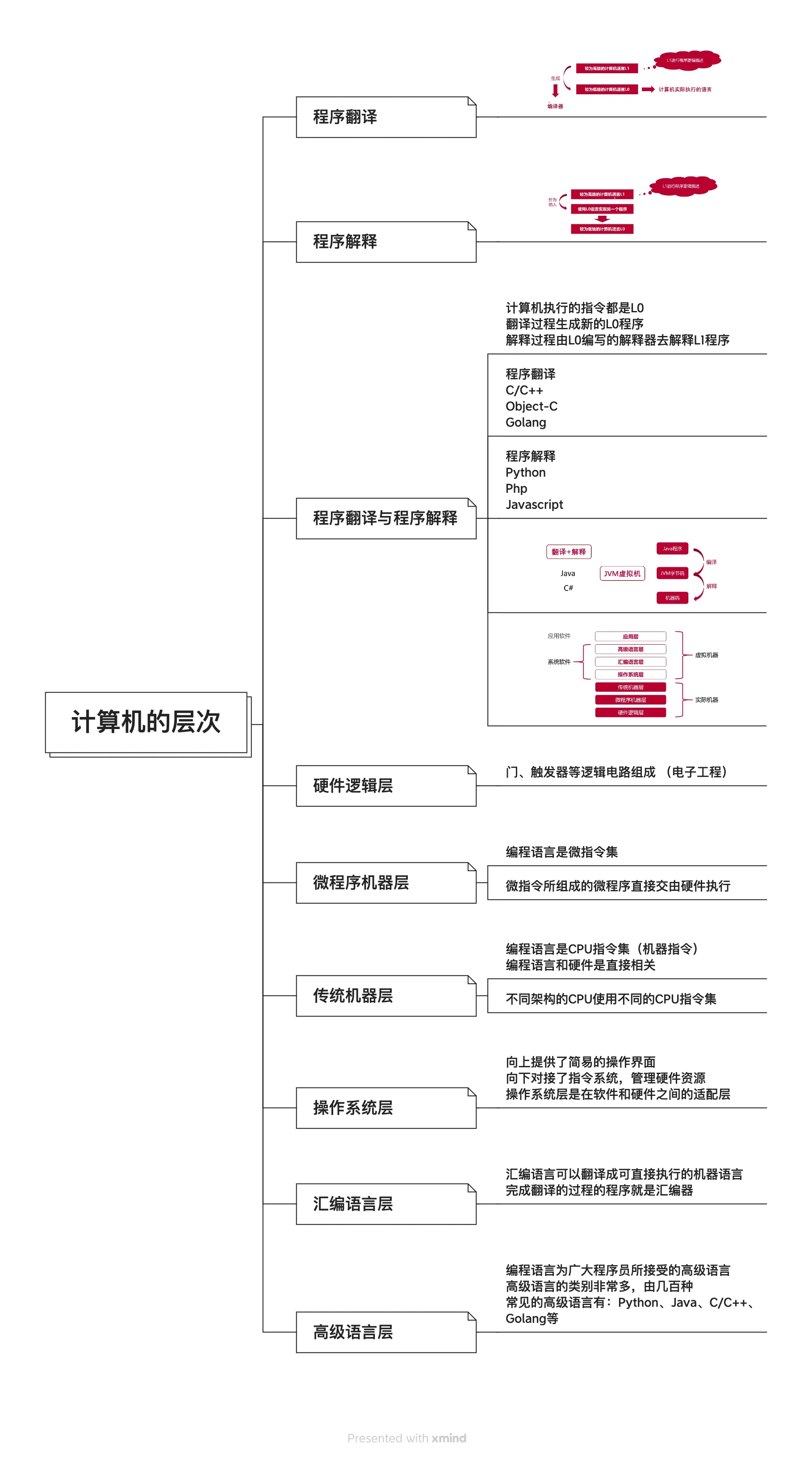

计算机的层次

计量单位

- 容量单位

- 速率单位

容量单位

- 在物理层面,高低电平记录信息, 用0/1记录状态

| - | bit | Byte | KB | MB | GB | TB | PB | EB |

|---|---|---|---|---|---|---|---|---|

| 名称 | 比特位 | 字节 | 千字节 | 兆字节 | 吉字节 | 太字节 | 拍字节 | 艾字节 |

| 比例 | - | 8bits | 1024B | 1024KB | 1024MB | 1024GB | 1024TB | 1024EB |

| 常见设备 | 门电路 | - | 寄存器 | 高速缓存 | 内存/硬盘 | 硬盘 | 云硬盘 | 数据仓库 |

为什么网上买的移动硬盘500G,格式化之后就只剩下465G ?

制作硬盘时有一个重要的指标 叫做扇区,在记录这个扇区时使用10进制更容易沟通协商,所以硬盘商一般采用10进制位标记容量

速度单位

-

网络速度

- 为什么电信拉的100M光纤,测试峰值速度只有

12M/s? 100M/s = 100Mbps = 100Mbit/s100Mbit/s=(100/8)MB/s=12.5MB/s

- 为什么电信拉的100M光纤,测试峰值速度只有

-

CPU速度

- CPU的速度一般体现为CPU的时钟频率

- CPU的时钟频率单位一般是赫兹(Hz)

- Hz其实就是秒分之一

- 它是每秒中的周期性变动重复次数的计量

- 主流CPU的始终频率都在2GHz以上

- 2GHz = 2*1000^3Hz = 每秒20亿次

计算机的组成

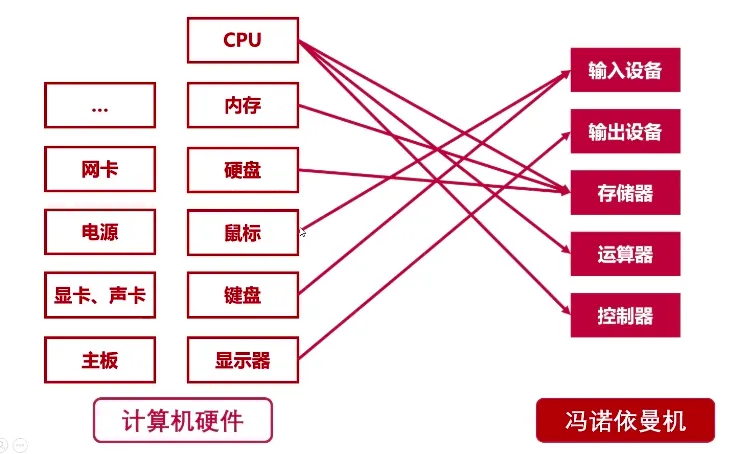

冯诺依曼计算机有哪些组成?

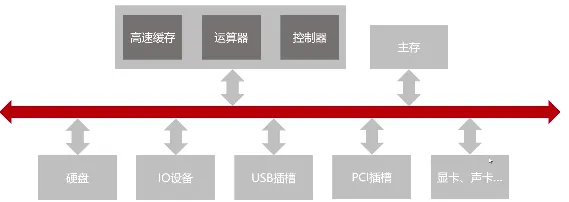

- 计算机的总线与IO设备

- 计算机的总线

- 计算机的输入/输出设备

- 计算机的存储器

- 计算机的高速存储器

- 计算机的主存储器与辅助存储器

- 计算机的CPU

- 计算机的指令系统 计算机的运算器

- 计算机的控制器 指令执行过程

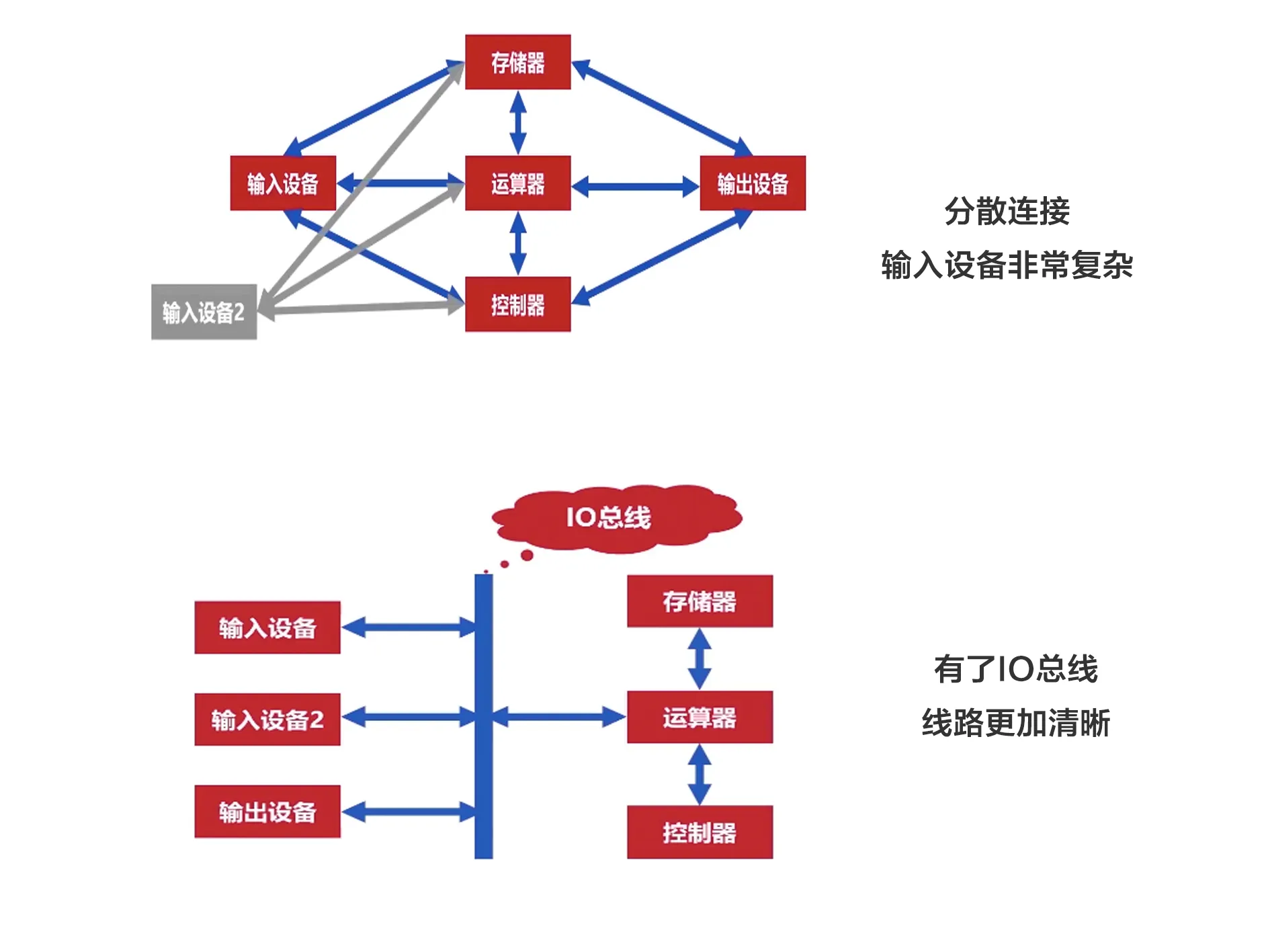

总线

总线是连接计算机不同设备,解决它们之间的通信问题。

比较常见的一个案例是 USB = Universal Serial Bus 通用串行总线

- 提供了对外连接的接口

- 不同设备可以通过USB接口进行连接

- 连接的标准,促使外围设备接口的统一

总线的好处

总线的分类

- 片内总线 (芯片内部的总线)

- 可以大大简化芯片内部的电路结构

- 系统总线

- 连接系统外围设备的总线

- 分类: 数据总线、地址总线、控制总线

数据总线

- 双向传输各个部件的数据信息

- 数据总线的位数(总线宽度) 是数据总线的重要参数

- 一般与CPU位数相同(32位、64位)

地址总线

- 指定源数据或目的数据在内存中的地址

- 地址总线的位数与存储单元有关

- 地址总线位数=n,寻址范围:

0~2**n

- 地址总线位数=n,寻址范围:

控制总线

- 控制总线是用来发出各种控制信号的传输线

- 控制信号经由控制总线从一个组件发给另外一个组件

- 控制总线可以监视不同组件之间的状态(就绪/未就绪)

总线的仲裁

为了解决总线使用权的冲突问题

为什么需要总线的仲裁?

- 假设计算机中内存需要和硬盘或IO设备交换数据, 这时候硬盘和IO设备都已经就绪了

- 那么总线由硬盘使用还是IO设备使用呢? 需要第三方仲裁器

总线的仲裁方法

- 链式查询

- 计时器定时查询

- 独立请求

输入输出设备

常见的输入设备

- 字符输入设备

- 键盘

- 薄膜键盘

- 图像输入设备

- 鼠标

- 数位板

- 扫描仪

常见的输入设备

- 图像输出设备

- 显示器

- 打印机

- 投影仪

输入输出接口的通用设计

- 数据线

- 是I/O设备与主机之间进行数据交换的传送线

- 单向传输数据线

- 双向传输数据线

- 状态线

- IO设备状态向主机报告的信号线

- 查询设备是否已经正常连接并就绪

- 查询设备是否已经被占用

- 命令线

- CPU向设备发送命令的信号线

- 发送读写信号

- 发送启动停止信号

- 设备选择线

- 主机选择I/O设备进行操作的信号线

- 对连在总线上的设备进行选择

输入输出接口的通用设计

- IO设备状态向主机报告的信号线

- 查询设备是否已经正常连接并就绪

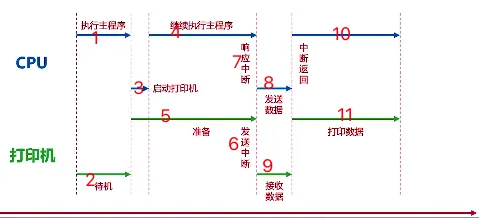

CPU与IO设备的通信方法

- 程序中断

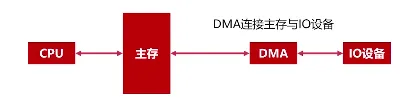

- DMA (直接存储器访问)

先了解一个前提: CPU速度与IO设备速度不一致(CPU速度要快很多)

程序中断示例

补充: 7 响应中断并非同步进行,

程序中断

- 当外围IO设备就绪时,向CPU发出中断信号

- CPU有专门的电路响应中断信号

程序中断提供了低速设备通知CPU的一种异步的方式,CPU可以高速运转同时兼顾低速设备的响应。

缺点: 频繁打断CPU 也会影响CPU的执行效率

DMA (直接存储器访问)

- 当主存与IO设备交换信息时,不需要中断CPU, 可以提高CPU的效率

- 在硬盘和外界显卡都有DMA设备

计算机的存储器

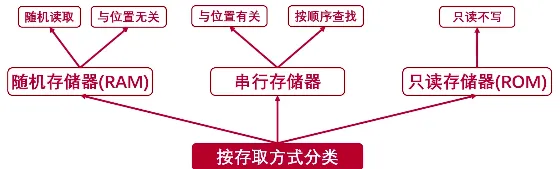

存储器的分类

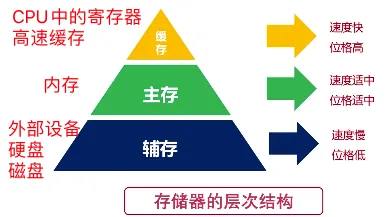

存储器的层次结构

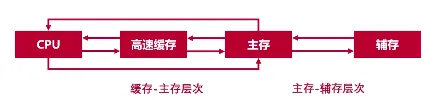

- 这种层次结构,它是利用局部性原理,在CPU与主存之间增加一层速度快(容量小)的Cache,以解决主存速度不足的问题。

- 速度快容量小的catche即高速缓存,因为有高速缓存的存在,我们使用一定的策略尽量让CPU访问高速缓存中的数据

局部性原理是指CPU访问存储器时,无论是存取指令 、还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中。

同样 局部性原理 也可以用于解决主存容量不足的问题 具体是在主存之外增加辅助存储器(磁盘、SD卡、U盘)

主存储器和辅助存储器

计算机断电,为什么内存数据丢失,而硬盘数据不会丢失?

主存储器--内存

- RAM (随机存取存储器:Random Access Memory)

- RAM通过电容存储数据,必须隔一段时间刷新一次

- 如果掉电,那么一段时间后将会丢失所有数据

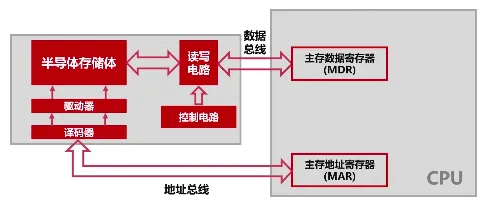

内存与CPU通信的方式

不同位数的操作系统对内存的支持是不一样的

- 比如 32位系统, 最多支持

2**32 = 4*2**30 = 4GB,即使加更多的内存也是没用的,因为他的地址总线最多是32位,所以它的寻址范围最多是4GB大小 - 64位系统 最多支持

2**64 = 2**34*2**30 = 2**34GB

主存储器 --内存 辅助存储器 -- 磁盘

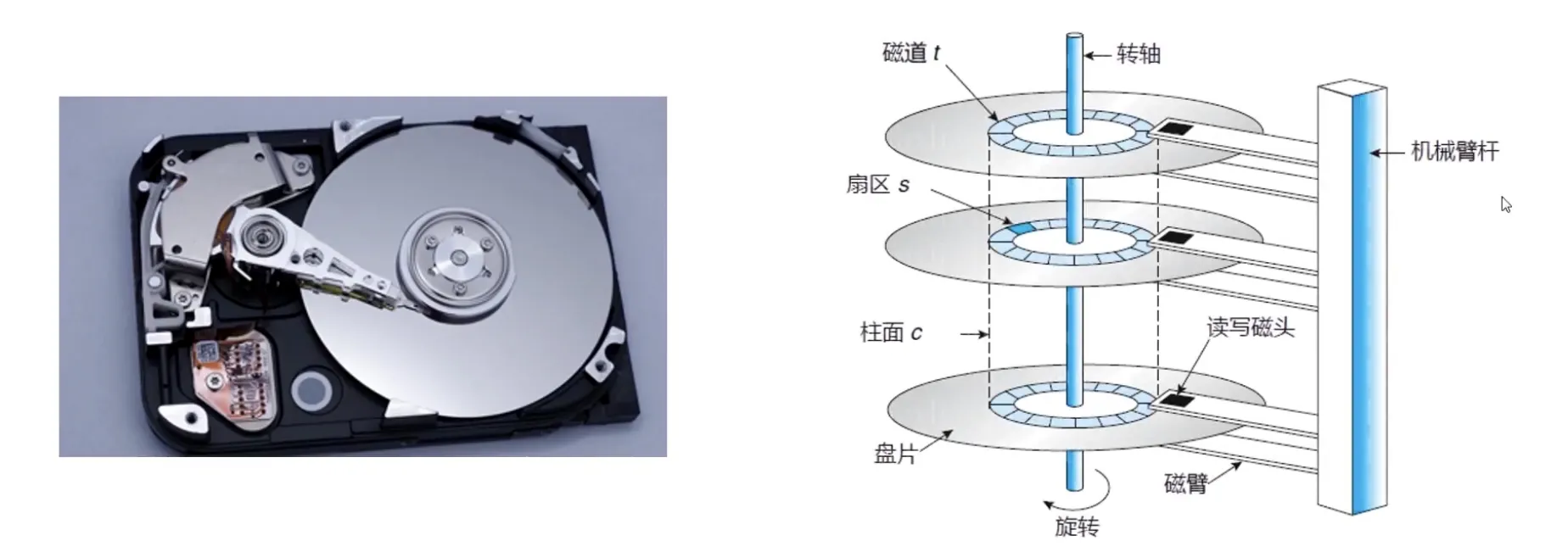

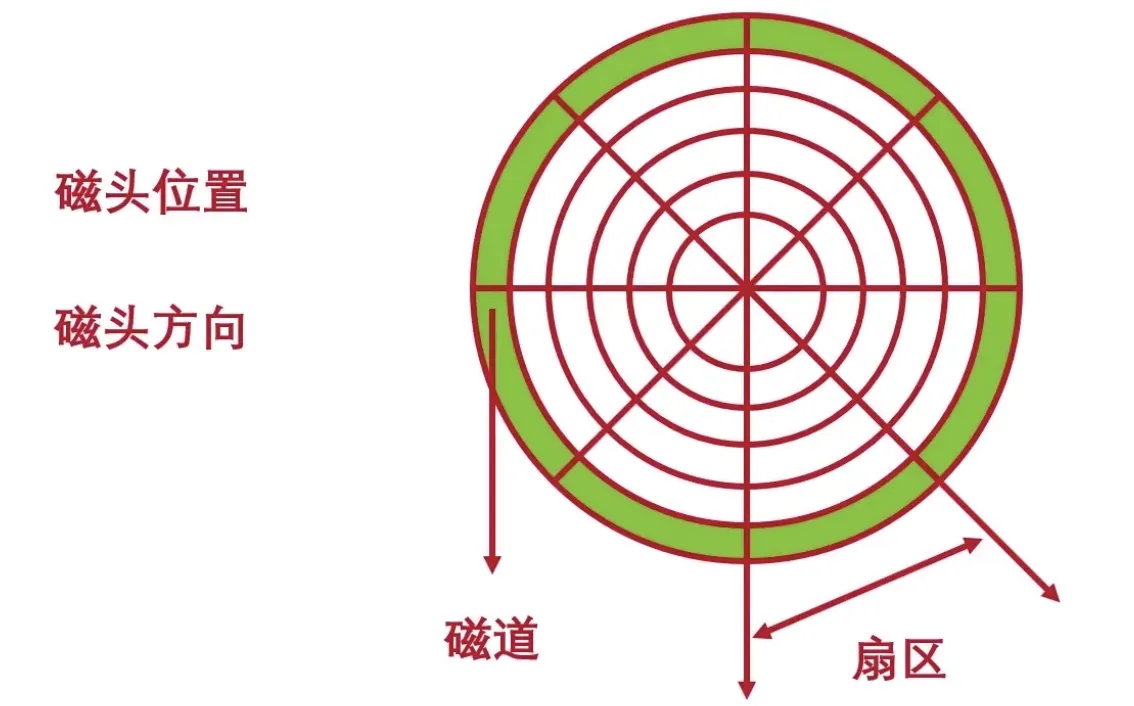

磁盘

- 表面是可磁化的硬磁特性材料

- 移动磁头径向运动读取磁道信息

磁盘服务算法

- 先来先服务算法

- 最短寻道时间优先

- 扫描算法(电梯算法)

- 循环扫描算法

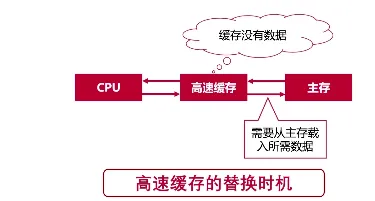

高速缓存的工作原理

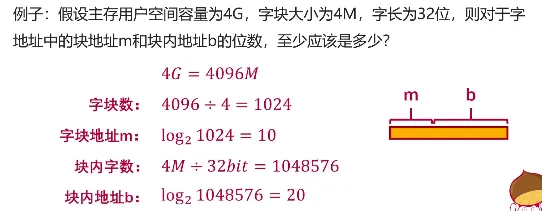

高速缓存是如何寻址的?

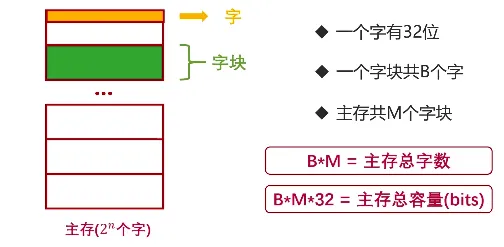

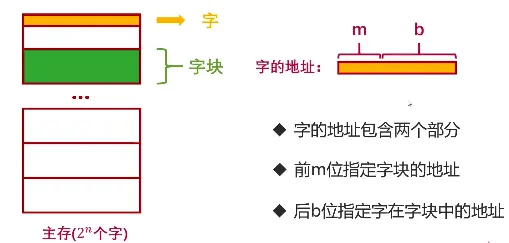

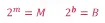

- 字 是指存放在一个存储单元中的二进制代码组合

- 字块 存储在连续的存储单元中而被看作是一个单元的一组字

主存的容量远大于高速缓存中的容量,缓存的内容是主存内容的复制

- CPU取数据有两种情况,如果缓存中有从缓存中取,如果缓存中没有从主存里拿。

- 因为高速缓存要比内存快很多,所以要提高高速缓存的利用率。

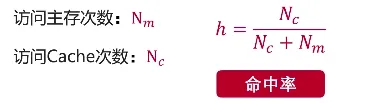

- 可与使用“命中率”和“访问效率”来刻画缓存的利用率

那么如何提高缓存的 命中率 或 访问效率呢?

高速缓存的替换策略

- 随机算法

- 先进先出算法(FIFO)

- 把高速缓存看做是一个先进先出的队列

- 优先替换最先进入队列的字块

- 最不经常使用算法(LFU)

- 优先淘汰最不经常使用的字块

- 需要额外空间记录字块的使用频率

- 最近最少使用算法(LRU)

- 优先淘汰一段时间内没有使用的字块

- 从队列尾部淘汰节点

- 与FIFO的区别, 读取的时候 会把节点提取到队列头部

- 有多种实现方法,一般使用双向链表

- 把当前访问节点置于链表前面(保证链表头部节点是最近使用的)

- 优先淘汰一段时间内没有使用的字块

关于这几种算法,后面在我的数据结构与算法文章中讲解

计算机的指令系统

机器指令的形式

- 机器指令主要由两部分组成:操作码、地址码

- 操作码字段 地址码字段

- 操作码指明指令所要完成的操作

- 操作码的位数反映了机器的操作种类

- 地址码直接给出操作数或者操作数的地址

- 分三地址指令、二地址指令和一地址指令

地址码类型

- 三地址指令

| 操作码(OP) | addr1 | addr2 | addr3 |

|---|

(addr1)OP(addr2) → (addr3)

- 二地址指令

| 操作码(OP) | addr1 | addr2 |

|---|

(addr1)OP(addr2) → (addr1)或(addr2)

- 一地址指令

| 操作码(OP) | addr1 |

|---|

(addr1)OP→ (addr1) (addr1)OP(ACC) → (addr1)

- 零地址指令

- 空操作、停机操作、中断返回操作等

机器指令的操作类型

- 数据传输

- 寄存器之间、寄存器与存储单元、存储单元之间传

- 数据读写、交换地址数据、清零置一等操作

- 算术逻辑操作

- 操作数之间的加减乘除运算

- 操作数的与或非等逻辑位运算

- 移位操作

- 数据左移(乘2)、数据右移(除2)

- 完成数据在算术逻辑单元的必要操作

- 控制指令

- 等待指令、停机指令、空操作指令、中断指令等

机器指令的寻址方式

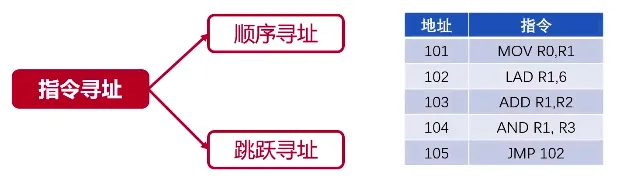

个人理解 寻址 类似解析汇编语言,它包括两部分内容 指令寻址 和 数据寻址

指令寻址有 顺序寻址 和 跳跃寻址 两种方式

- 顺序寻址 依次执行 101 - 102 - 103 - 104 - 105

- 跳跃寻址 执行了105后跳回102继续执行 105 - 102

数据寻址的方式

- 立即寻址

- 指令直接获取操作数

- 无需访问存储器

- 直接寻址

- 直接给出操作数载主存的地址

- 寻找操作数简单,无需计算数据地址

- 间接寻址

- 指令地址码给出的是操作数地址的地址

- 需要访问一次或多次主存来获取操作数

| 寻址方式 | 优点 | 缺点 |

|---|---|---|

| 直接寻址 | 速度快 | 地址码位数限制操作数表示范围 |

| 间接寻址 | 寻找操作数简单 | 地址码位数限制操作数寻址范围 |

| 间接寻址 | 操作数寻址范围大 | 速度较慢 |

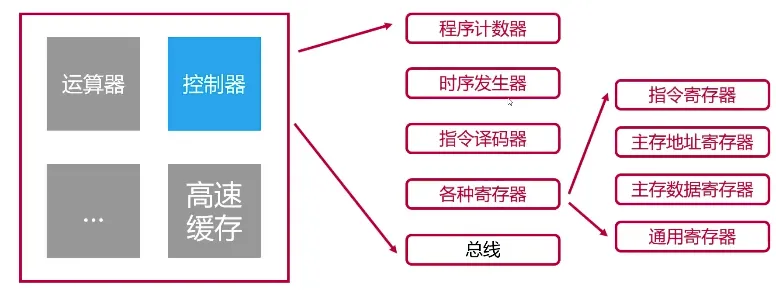

控制器

控制器是协调和控制计算机运行的

-

程序计数器

- 程序计数器用来存储下一条指令的地址

- 循环从程序计数器中拿出指令

- 当指令被拿出时,指向下一条指令

-

时序发生器

- 电气工程领域,用于发送时序脉冲

- CPU依据不同的时序脉冲有节奏的进行工作

-

指令译码器

- 指令译码器是控制器的主要部件之一

- 计算机指令由操作码和地址码组成

- 翻译操作码对应的操作以及控制传输地址码对应的数据

-

指令寄存器

- 指令寄存器也是控制器的主要部件之一

- 从主存或高速缓存取计算机指令

-

主存地址寄存器

- 保存当前CPU正要访问的内存单元的地址

-

主存数据寄存器

- 保存当前CPU正要读或写的主存数据

-

通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU的运算中间结果

- 容量比一般专用寄存器要大

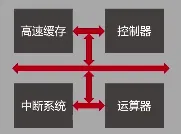

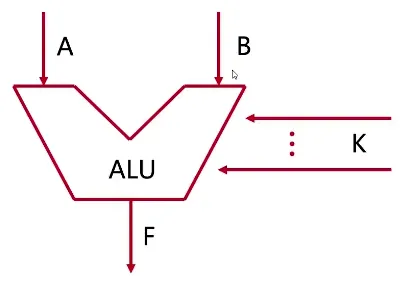

运算器

运算器是用来进行数据运算和加工的,它包括 数据缓冲器、ALU、通用寄存器、状态字寄存器

- 数据缓冲期

- 分为输入缓冲和输出缓冲

- 输入缓冲暂时存放外设送过来的数据

- 输出缓冲暂时存放送往外设的数据

- ALU

- ALU:算术逻辑单元,是运算器的主要组成

- 常见的位运算(左右移、与或非等)

- 算术运算(加减乘除等)

-

- 状态字寄存器

- 存放运算状态(条件码、进位、溢出、结果正负等)

- 存放运算控制信息(调试跟踪标记位、允许中断位等)

- 通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU的运算中间结果

- 容量比一般专用寄存器要大

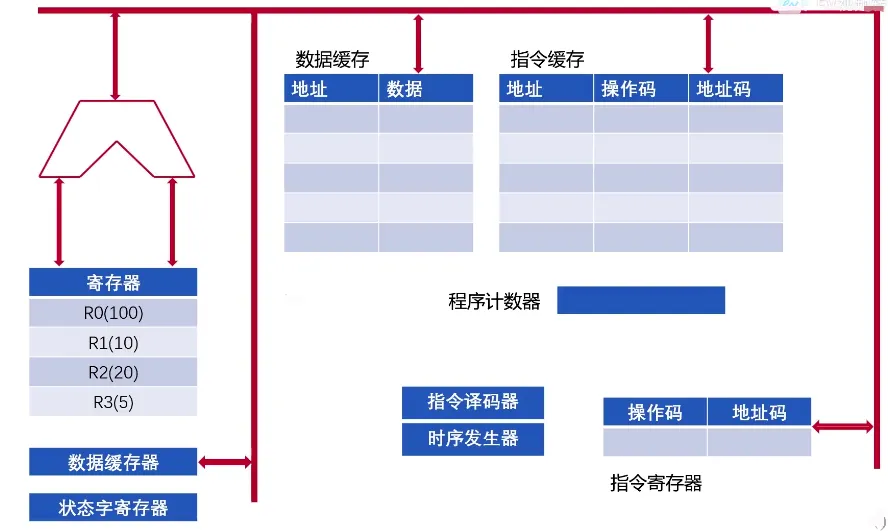

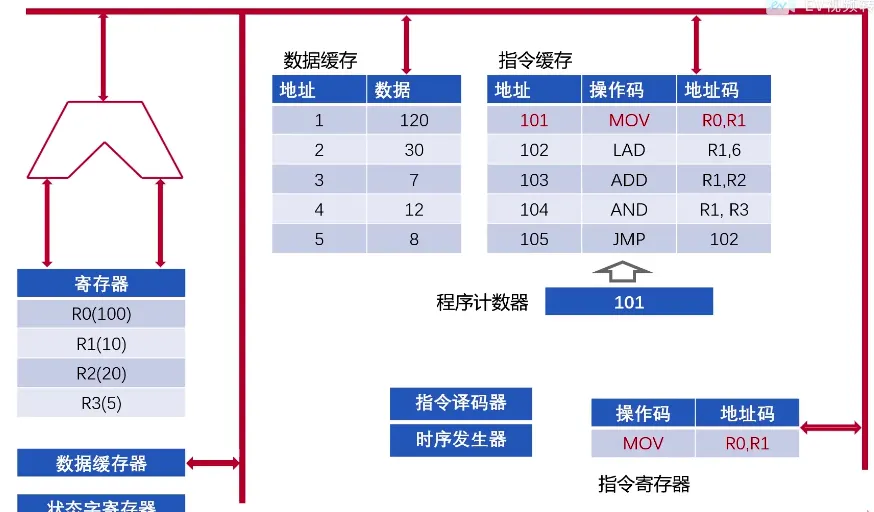

指令的执行过程

取指令 --> 分析指令 --> 执行指令

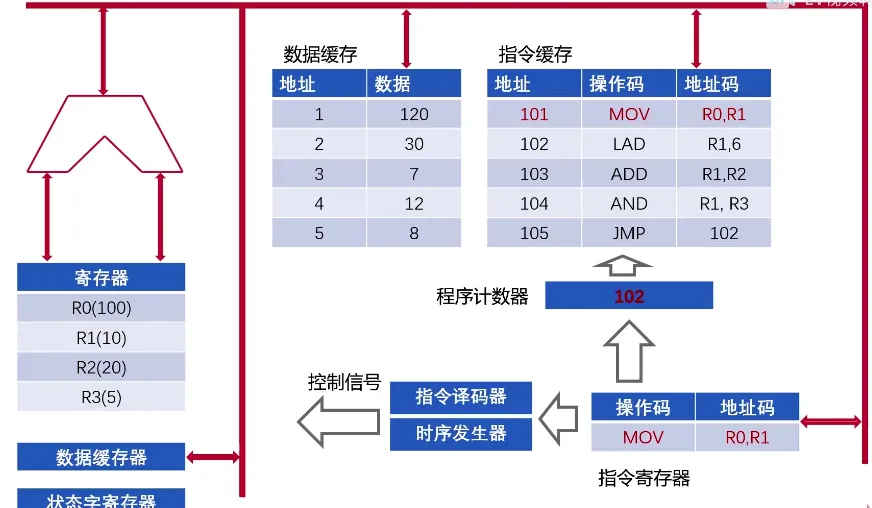

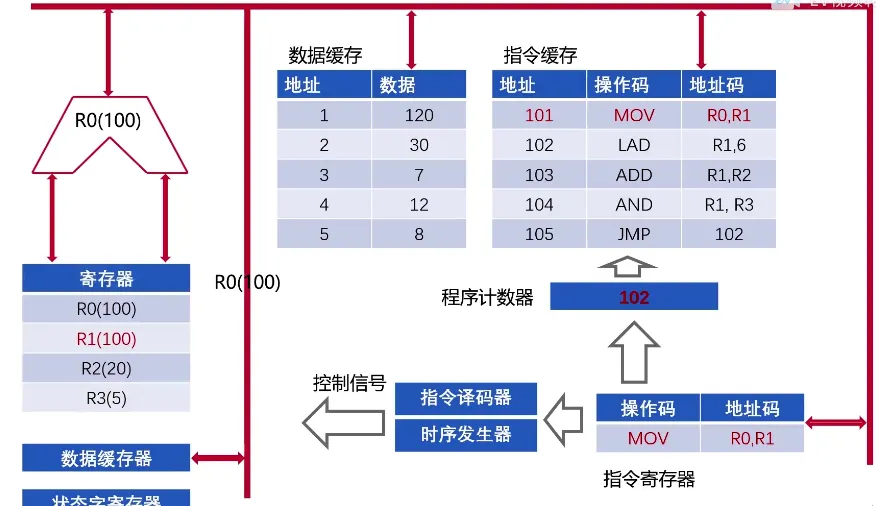

- 先来看一下指令执行过程所涉及的元件

- 左边一列 是运算器

- 上面的两块(数据缓存&指令缓存)是高速缓存

- 右下角三块 是 控制器

- 所有原件通过总线连接

执行过程

- 将数据缓存起来

- 程序计数器 缓存当前需要执行的指令的地址

- 指令寄存器 取出当前指令的操作吗和地址码

- 指令计数器并不知道具体内容,需要将指令发送到指令译码器中, 同事程序计数器+1

- 指令译码器 知道要进行的操作 将 R1 数据 移到 R0中, 然后发出控制信号, 通过片内总线来到运算器里面

- ALU运算线加载R0 (值从寄存器去除) ,然后送到片内总线 ,再送到数据缓存其中,数据缓存起将R0的数据复制到R1中去

- 完成了当前指令 按同样的顺序执行下一条指令。

上述流程存在一个问题, 控制器和运算器不能同时运行, 这导致CPU的利用率不高

解决方案: CPU 的流水线设计

本文作者:郭敬文

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!